# AI Compute Architecture and Evolution Trends

Bor-Sung Liang, Senior Member, IEEE

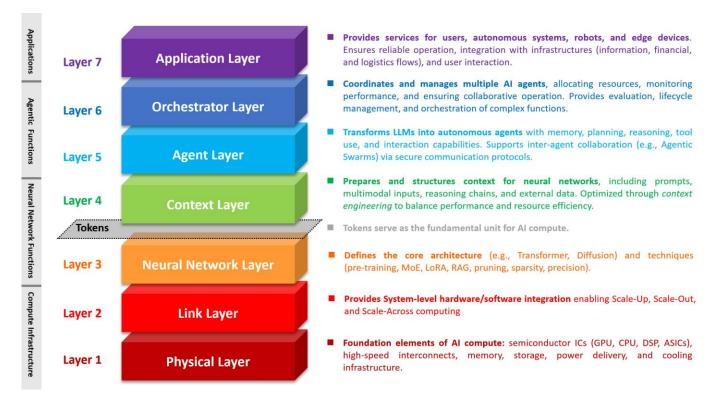

Fig. 1 Seven-layer Model for AI Compute Architecture

Abstract—The focus of AI development has shifted from academic research to practical applications. However, AI development faces numerous challenges at various levels. This article will attempt to analyze the opportunities and challenges of AI from several different perspectives using a structured approach. This article proposes a seven-layer model for AI compute architecture, including Physical Layer, Link Layer, Neural Network Layer, Context Layer, Agent Layer, Orchestrator Layer, and Application Layer, from bottom to top. It also explains how AI computing has evolved into this 7-layer architecture through the three-stage evolution on large-scale language models (LLMs). For each layer, we describe the development trajectory and key technologies. In Layers 1 and 2 we discuss AI computing issues and the impact of Scale-Up and Scale-Out strategies on computing architecture. In Layer 3 we explore two different development paths for LLMs. In Layer 4 we discuss the impact of contextual memory on LLMs and compares it to traditional processor memory. In Layers 5 to 7 we

Bor-Sung Liang is with MediaTek Inc., Hsinchu Science Park, Taiwan (e-mail: bs.liang@mediatek.com or bsliang@gmail.com). He is also concurrently serving as a Visiting Professor at CSIE (Department of Computer Science and Information Engineering) and GIEE (Graduate Institute of Electronics Engineering), EECS (College of Electrical Engineering and Computer Science) and GSAT (Graduate School of Advanced Technology) in National Taiwan University, as well as a Visiting Professor at ECE (College of Electrical and Computer Engineering) in National Yang Ming Chiao Tung University.

discuss the trends of AI agents and explore the issues in evolution from a single AI agent to an AI-based ecosystem, and their impact on the AI industry. Furthermore, AI development involves not only technical challenges but also the economic issues to build self-sustainable ecosystem. This article analyzes the internet industry to provide predictions on the future trajectory of AI development.

Index Terms— Artificial Intelligence (AI), Computing Architecture, Large Language Models (LLMs), Neural Networks, Multi-Agent Systems, AI Ecosystems, Scalability, Energy Efficiency

#### I. INTRODUCTION

HE focus of artificial intelligence (AI) development has shifted from academic research to practical applications. This wave of AI advancement began with the AlexNet project in 2012 [1], which demonstrated the transformative potential of deep neural networks. Following the introduction of the Transformer architecture in 2017 [2] and the discovery of scaling laws [3], the number of model parameters and computational requirements increased dramatically, igniting a global race to develop large language models (LLMs). By 2022, the release of ChatGPT drew

worldwide attention and accelerated the emergence of generative AI. More recently, AI computing has expanded further into the domains of Agentic AI and Physical AI, signaling a broader evolution toward intelligent and autonomous systems.

The rapid progress of AI holds the potential to significantly boost global productivity. If a sustainable AI-based ecosystem can be successfully established, its economic and societal impact may rival that of previous industrial revolutions. However, AI development also faces major challenges—ranging from scaling computational power and improving energy efficiency, to enhancing training and inference for increasingly complex neural networks, building effective AI agents, and establishing viable business models that sustain continuous innovation. This article provides a structured analysis of these opportunities and challenges, illustrating how AI computing has evolved into a multi-layered architecture that integrates hardware, algorithms, and intelligent systems into a coherent technological framework.

To provide a systematic understanding of how AI systems evolve and interact across different levels of technology, this article proposes a seven-layer AI computing architecture model, inspired by the conceptual clarity of the *Open Systems Interconnection (OSI) reference model* [4]. Just as the OSI model standardized communication across heterogeneous networks, the proposed framework aims to structure the complex and rapidly expanding ecosystem of AI computing.

Several prior studies have attempted to describe AI or large language model (LLM) infrastructures in layered forms [5], [6]. However, most of these works concentrate on methodologies for software systems and application development. In contrast, this work extends the abstraction to encompass the hardware, software, and system architecture dimensions, providing an integrated perspective that connects physical compute infrastructure, neural architectures, contextual intelligence, agentic behaviors, orchestration mechanisms, and application ecosystems.

The proposed seven-layer AI compute model serves as a conceptual framework for analyzing the evolution of AI computing systems, rather than a prescriptive implementation architecture. Its purpose is to organize complex cross-layer interactions—from hardware to application ecosystems—into a coherent structure that facilitates comparative analysis and future research discussions.

The proposed model consists of seven layers, arranged from bottom to top:

1. **Physical Layer** – the foundational computing elements, including hardware components, energy sources, and local interconnects.

- 2. **Link Layer** the data and communication pathways that interconnect computing elements.

- 3. **Neural Network Layer** the core learning and inference mechanisms of deep neural network models.

- 4. **Context Layer** the representation and management of semantic and temporal context in computation.

- 5. **Agent Layer** the emergence of autonomous, task-oriented AI agents.

- 6. **Orchestrator Layer** the coordination and interaction among multiple AI agents and services.

- 7. **Application Layer** the integration of AI capabilities into user-facing products, services, and ecosystems.

Through this seven-layer framework, we can trace how AI computing has advanced from the early era of deep learning applications to today's multi-agent and orchestrated AI ecosystems. This structured perspective also enables a more systematic discussion of the opportunities, constraints, and future trajectories in AI computing architectures.

To clarify the scope of this article, we emphasize that large language models (LLMs) are used here as a **representative** use case to illustrate the broader evolution of AI compute architecture. AI spans diverse domains, including computer vision, reinforcement learning, generative models, and robotics, but LLMs provide the most data-rich and visible example of how compute requirements have rapidly scaled in recent years. By tracing the evolution of LLM compute, we highlight architectural trends such as scaling strategies, numerical representation, and multi-layer integration that extend across AI domains. This framing underscores the central theme of evolution in our title: from accelerating a single model, toward multi-agent systems and embodied AI that integrate into the wider AI-based ecosystem.

# II. SEVEN-LAYER MODEL FOR AI COMPUTING ARCHITECTURE

Artificial intelligence (AI) systems span multiple layers of technology, from physical hardware to user-facing applications. To describe this structure in a coherent way, we introduce a seven-layer model for AI computing architecture (Fig. 1). This framework highlights how different layers of computing interact to deliver AI capabilities and provides a systematic approach to analyzing the evolution of AI technologies.

This layered perspective serves two purposes. First, it enables a structured analysis of the development trajectory of each layer, making it possible to trace technological progress from semiconductor design to AI-driven ecosystems. Second, it provides a unified framework for comparing strategies, such as *Scale-Up* versus *Scale-Out* [7], and for identifying cross-layer challenges in scalability, energy efficiency, and system integration. By adopting this abstraction, we can better interpret how AI computing has advanced and anticipate how future innovations will reshape the overall ecosystem.

#### Layer 1: Physical Layer

The Physical Layer forms the foundation of AI computing architecture. It encompasses the semiconductor integrated circuits (ICs) that execute computation, including GPUs, CPUs, DSPs, FPGAs, AI accelerators, and application-specific integrated circuits (ASICs), as well as supporting infrastructure such as high-speed interconnects, high-bandwidth memory, data storage, power delivery, and thermal management systems.

Advances in semiconductor process technology and domain-specific architectures (DSAs) [8] have been central to sustaining AI performance growth. While Moore's Law and general-purpose CPUs once drove progress in computing, the scale of modern AI workloads now requires specialized accelerators optimized for tensor operations and massive parallelism. These advances, coupled with innovations in memory hierarchies and advanced packaging technologies, form the critical basis for AI scalability. Nevertheless, *energy efficiency* remains a fundamental challenge at this layer, as power delivery and cooling demands have increased significantly with model size and system complexity.

## Layer 2: Link Layer

The Link Layer enables large-scale integration of computing resources by connecting and managing thousands to millions of processing units. It includes both hardware interconnects, such as high-speed networks, switches, and optical links, and the system software stack responsible for communication, synchronization, and distributed workload management.

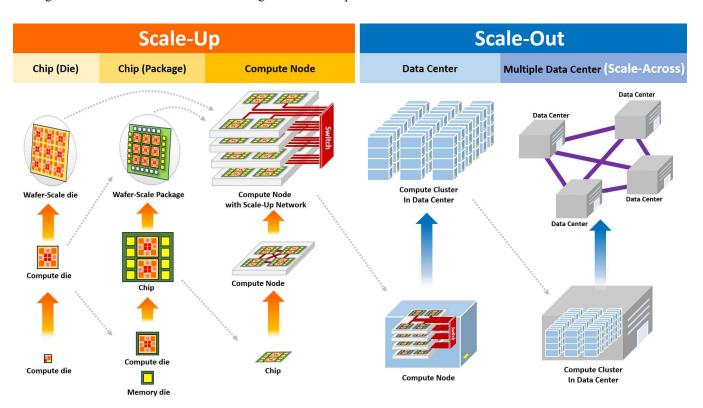

There are two key strategies to scale computing: **Scale-Up**, which seeks performance gains within a single compute node by (i) improving individual chips through advanced design and process technologies, (ii) integrating multiple dies within a chip package, or (iii) interconnecting multiple chips inside a compute node; and **Scale-Out**, which aggregates massive numbers of compute nodes into large-scale clusters to meet the exponential growth of AI workloads. The Scale-Out approach has become indispensable for training and deploying large language models, but it also amplifies concerns regarding latency, energy consumption, and overall system efficiency.

Efficient orchestration of compute nodes, memory, and interconnect bandwidth at this layer directly determines the capability and sustainability of AI computing systems. In addition, a concept known as **Scale-Across** [9] has been proposed to extend the Scale-Out strategy across geographically distributed data centers, thereby integrating compute clusters over long distances.

### **Layer 3: Neural Network Layer**

The Neural Network Layer represents the core of AI capability, defining the architectures, parameterization, and learning mechanisms that drive modern artificial intelligence. Early breakthroughs such as AlexNet (2012) [1] demonstrated the power of deep neural networks. This momentum accelerated with the introduction of the Transformer architecture (2017) [2] and the discovery of scaling laws [3], which revealed that model performance improves predictably with increases in parameter size, training data, and compute resources. These developments ignited the global race to build increasingly large-scale large language models (LLMs).

To enhance neural network efficiency and capability, numerous techniques have been developed, including pretraining, fine-tuning, low-rank adaptation (LoRA) [10] mixture-of-experts (MoE) models [11], and retrievalaugmented generation (RAG) [12]. In addition, methods such as sparsity [13], pruning [14], mixed-precision arithmetic [15], speculative decoding [16], and key-value (KV) caching [17] have been introduced to improve both computational efficiency and energy consumption. A key trend within this layer is the emergence of two distinct development trajectories. One trajectory continues to scale LLMs upward to push the boundaries of AI capabilities. The other trajectory focuses on distillation into smaller, domain-specific LLMs [18], which significantly reduce inference costs while enabling deployment on resource-constrained devices. These compact LLMs are increasingly viewed as essential building blocks for constructing AI agents, providing a balance between performance, efficiency, and accessibility. Together, these advances have shaped the practical deployment of LLMs at massive scale.

At the Neural Network Layer, information is represented and processed as **tokens**, which serve as the fundamental units of AI computation. Tokens bridge natural information and neural architectures, encompassing language units in text, image patches or feature maps in computer vision, and audio frames in speech processing. This reliance on tokenization and detokenization distinguishes AI computing from prior computing paradigms, making token-based processing a defining characteristic of this layer

•

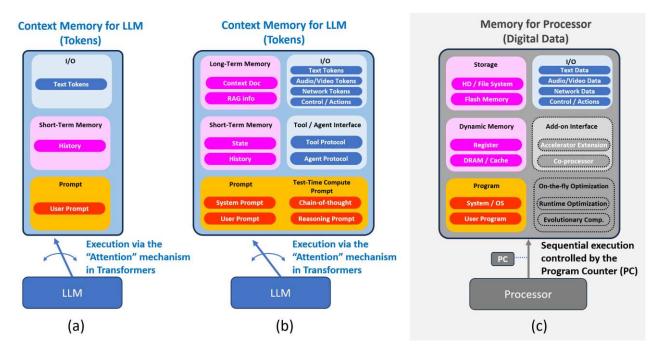

## Layer 4: Context Layer

The Context Layer defines how information is provided to, and interpreted by, neural networks such as LLMs. Unlike traditional processors that rely on fixed memory hierarchies, AI systems depend on **context memory**—a dynamic window of tokens that captures relevant information for reasoning and response generation.

In practice, the context supplied to an LLM may include prompts, documents, images, audio, video, multimodal data, or sensor inputs. These diverse inputs are converted into tokens through **tokenization**, processed by the neural network, and then reconverted into human-readable outputs through **detokenization**. The length and richness of the context window strongly influence model performance: a larger context window typically improves reasoning and recall but also incurs substantially higher computational and memory costs.

A variety of methods have been proposed to optimize the use of context. Techniques such as prompt engineering [19], test-time compute [20], reasoning strategies including chain-of-thought (CoT) [21] and tree-of-thought (ToT) [22], as well as context engineering [23] [24], aim to maximize model output quality while reducing hallucinations and resource overhead. These techniques highlight that the Context Layer plays a far more proactive role in shaping neural network performance than memory management in traditional computing systems.

A useful way to illustrate this shift is by comparing traditional processor memory with AI context memory:

- Traditional processors play a passive role in computing. They are controlled by software programs and operate under predefined instruction sequences. Memory in this paradigm is largely static: it stores data and instructions, which are fetched and executed according to fixed control logic.

- AI systems, in contrast, treat context memory as an active workspace. Output tokens are generated according to the model's attention mechanism, and these tokens can also feed back to influence subsequent attention, effectively creating a self-modifying process. In other words, context memory actively participates in shaping the system's behavior, rather than serving merely as passive storage.

This distinction underscores a fundamental paradigm shift: whereas memory in traditional computing serves as a static repository, context memory in AI functions as a dynamic substrate for reasoning and adaptation.

## **Layer 5: Agent Layer**

The Agent Layer converts a capable neural model, typically an LLM, into a **goal-oriented system** that can perceive context, plan actions, use tools, and interact with the external world. Beyond generating text, an AI agent maintains short-term memory and long-term memory [25], retrieves episodic/semantic memory from external stores, decomposes tasks, selects tools or APIs [26] [27], and executes actions under constraints such as cost, latency, safety, and authorization.

In practical deployments, an agent stack commonly includes:

- **Memory**: short-term scratchpads, long-term vector or key-value stores, and preference/state profiles.

- Reasoning & Planning: task decomposition, reflection/ critique loops, self-verification.

- **Tool Use**: function call, API invocation, database queries, code execution.

- Action: web or device control, robot control, interaction.

- Multimodality: tokenize text, images, audio, video, or sensor streams into context, and de-tokenize for output

- Safety, Policy, and Authorization: role-based access, personally identifiable information (PII) filtering, credit limit control, guardrails, security.

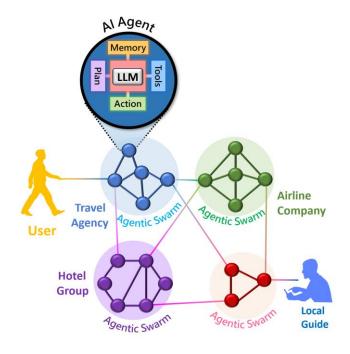

As tasks grow in scope, multiple agents coordinate to deliver end-to-end capabilities. This naturally leads to the concept of **Agentic Swarms** [28] [29] [30], where teams of interoperable agents collaborate across organizational or platform boundaries. Inter-agent communication benefits from emerging **agent protocols**, which for capability discovery, authentication, message schemas, and trust/credit exchange, enabling standardized and auditable interactions among heterogeneous agents.

The Agent Layer thus enables LLMs to connect with other AI agents, forming swarms composed of many specialized agents that collectively provide complex functionality. Several protocols for this purpose are under active development, including Anthropic's Model Context Protocol (MCP) [31], Google's A2A (Agent-to-Agent) [32], OpenAI Swarm [33], and IBM's Agent Communication Protocol (ACP) [34].

## **Layer 6: Orchestrator Layer**

The Orchestrator Layer coordinates the execution of tasks across multiple AI agents, resources, and services. While individual agents (Layer 5) can operate autonomously, orchestrators provide the system-level governance that enables agents to work together in scalable, reliable, and auditable ways.

At this layer, orchestration performs several critical roles:

- Task Scheduling and Decomposition: assigning subtasks to appropriate agents, ranking candidate solutions, and aggregating outputs.

- Agent Evaluation: benchmark [35] [36], selection, deployment, and tracking of performance records.

- Management: allocating compute, Resource memory, storage, and network bandwidth across agents to balance latency, throughput, and cost.

- Monitoring and Control: tracking execution status, collecting performance metrics, and providing feedback signals to improve agent selection and learning.

- Fault Tolerance and Recovery: detecting failures, retrying failed actions, and reassigning tasks dynamically to ensure robustness.

- Policy Enforcement: implementing guardrails such as safety constraints, access controls, audit logs, and compliance checks.

In modern deployments, orchestrators function much like operating systems for agents—they provide the substrate where heterogeneous AI services can coexist and collaborate. Emerging frameworks increasingly combine workflow engines, distributed schedulers, and reinforcement learning controllers to improve orchestration efficiency. For example, multi-agent orchestration has been studied in the context of cloud computing, robotics, and autonomous systems, and these methods are now being extended to AI agents at scale [37] [38] [39] [40].

Orchestration enables agent ecosystems to transition from ad hoc collections of tools into structured, reliable services. Orchestrators determine which agents should be activated, when they should be invoked, how their results should be validated, and how trade-offs between speed, cost, and accuracy should be resolved. This governance ensures that the overall AI system behaves predictably and meets humancentered requirements.

## **Layer 7: Application Layer**

The Application Layer represents the stage where AI capabilities are transformed into real-world products, services, and ecosystems that directly impact users, organizations, and industries. It is the most visible layer of the seven-layer model, where advances in computing, neural networks, context management, and agents converge into applications that provide tangible value.

At this layer, integration and trust emerge as defining challenges. AI applications must align with user expectations for accuracy, safety, fairness, transparency, and accountability. Business considerations are equally critical: successful applications require sustainable economic models, regulatory compliance, and interoperability with existing digital infrastructure.

Another defining trend is the shift from single AI tools to ecosystems of orchestrated AI-based services. For example, an enterprise workflow may combine multiple agents for retrieval, reasoning, verification, and reporting, all coordinated by orchestrators to meet predefined service-level objectives. This convergence underscores the importance of cross-layer design: choices at the physical, link, network, and agent layers ultimately shape the reliability, efficiency, and adoption of AI applications, forming the foundation of AI-based ecosystems. Summary of Seven-Layer Model of AI Compute

# Architecture

The seven-layer AI computing architecture provides a structured framework for analyzing the evolution of artificial intelligence, from its physical computing foundations to largescale applications. Each layer highlights a distinct set of challenges and opportunities—ranging from hardware scalability and interconnect efficiency, to neural architectures, contextual reasoning, agent behaviors, orchestration, and ecosystem-level integration. Together, these layers illustrate how advances across multiple domains converge to form modern AI systems.

By adopting this layered perspective, we can better interpret past developments, identify current bottlenecks, and anticipate future directions in AI computing. More importantly, the framework emphasizes that sustainable progress will require cross-layer design and coordination. The interplay between hardware. algorithms, orchestration mechanisms, applications will ultimately determine not only the performance of AI systems, but also their trustworthiness, accessibility, and long-term societal impact—shaping the future of AI-based ecosystems.

#### III. THE EVOLUTION OF LLMs (TOP-DOWN VIEW)

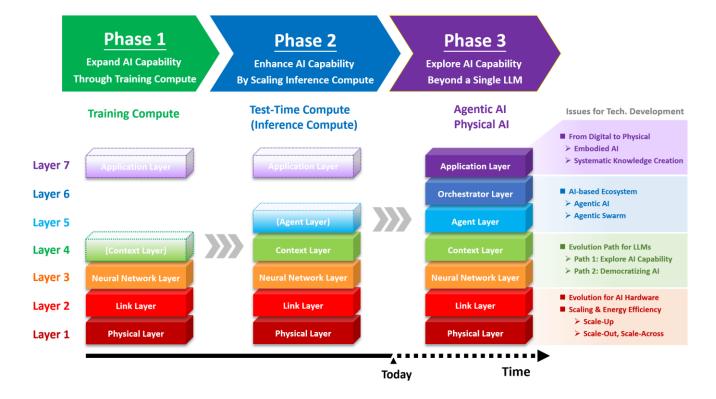

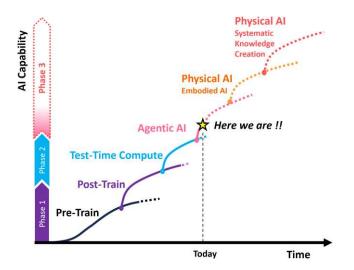

Fig. 2 conceptually illustrates the evolutionary trajectory of AI compute. Early development focused on scaling single models, exemplified by large language models (LLMs). Subsequent stages extend beyond single-model training and inference, toward agentic AI and physical AI that interact with the real world. LLMs are thus highlighted not as the sole definition of AI, but as a representative use case that makes the broader evolutionary dynamics of AI compute more concrete.

Building on this framework, the evolution of LLMs can be described in three phases. Phase 1 explores the scaling of single models through massive compute investment during training. Phase 2 emphasizes test-time compute for reasoning, while also enabling smaller LLMs that democratize AI applications. Phase 3 moves beyond single-model boundaries toward multi-agent systems (Agentic AI) and embodied intelligence (Physical AI), which together extend AI into both the knowledge and physical economies.

#### Phase 1: Expand AI Capability Through Training Compute

This period was characterized by exploring the capabilities of neural networks by scaling up the computational power available for AI training. Its impact spans Layers 1 to 3 of the compute architecture, and partially Layer 4 through prompting.

Since the release of AlexNet in 2012, researchers have consistently sought to enhance AI capabilities by adding more computing power. This trend accelerated following the introduction of the Transformer architecture in 2017, alongside the discovery of scaling laws, which showed that model performance improves predictably by increasing the number of parameters, the size of training datasets, and the amount of compute. As a result, the computational requirements for training AI systems have skyrocketed. For instance, training AlexNet in 2012 required roughly 10<sup>18</sup> FLOPs (floating-point operations), while training Gemini Ultra in 2023 required nearly 10<sup>26</sup> FLOPs [41]. In other words, within just a decade, the compute needed for state-of-the-art models increased by nearly eight orders of magnitude (10<sup>8</sup>).

Achieving this nearly 100-million-fold increase in compute within ten years could not have been accomplished through advanced semiconductor process alone. Historically, CPU performance growth driven by semiconductor scaling (Moore's Law) provided roughly a 100× increase per decade. Even with GPUs or AI-specific ASICs leveraging parallelism and tensor operations, a single chip might achieve a 1,000× to 10,000× increase per decade. Nevertheless, this still falls far short of the exponential growth required to train modern AI models. To meet these demands, the industry interconnecting chips—from dozens to hundreds of thousands, and in some cases millions—into large-scale compute clusters. This approach has driven explosive demand for advanced semiconductors.

Fig. 2 Three Phase Evolution of LLM, and Related Layers in Seven-Layer Model

Progress at Layer 1 (Physical Layer) has been fueled by advanced semiconductor processes and domain-specific architectures (DSAs). Layer 2 (Link Layer) plays a crucial role in enabling both Scale-Up and Scale-Out strategies, particularly by interconnecting vast numbers of GPUs and AI accelerators into distributed systems. At Layer 3 (Neural Network Layer), rapid growth in neural network architectures has directly driven compute demand, with innovations such as pre-training, post-training, and fine-tuning dramatically boosting performance.

Neural networks process information in the form of **tokens**, which have become the fundamental unit of both AI computation and performance measurement. Heavy reliance on tokens distinguishes AI compute architectures from prior computing paradigms. Moreover, prompting has emerged as a critical technique for improving the performance of large-scale language models, representing an early manifestation of **Layer 4 (Context Layer)**.

Phase 2: Enhance AI Capability By Scaling Inference Compute

In Phase 2, not only training compute but also **test-time compute** (**inference compute**) [42] emerged as a critical factor in enhancing AI capabilities. By increasing computational resources during the inference stage, neural networks can perform more sophisticated reasoning, improving their ability to handle complex tasks such as mathematics, programming, and planning. In this phase, prompting and context engineering for test-time compute became essential techniques, substantially increasing the importance of the **Layer 4 Context Layer**. In addition, LLMs began to be extended through AI agent techniques, linking this

phase partially to the Layer 5 Agent Layer (primarily in the form of single-LLM-based agent architectures).

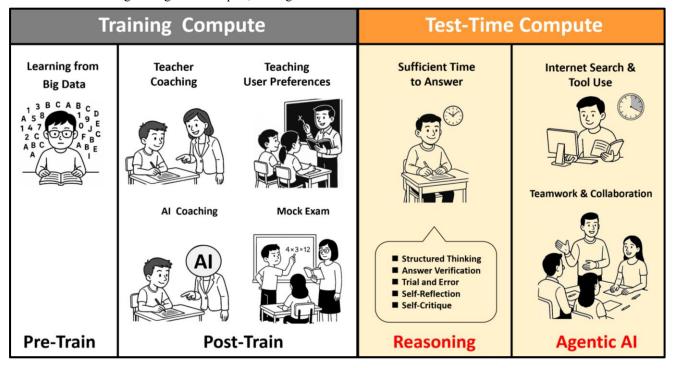

During Phase 1, LLMs typically produced immediate answers after receiving a prompt. While this approach worked for simple questions, it often led to errors on complex problems, especially those involving multiple conditions or hidden dependencies. By analogy, these early models resembled students who spend significant time studying but are forced to answer exam questions instantly, without the chance to think through their reasoning. Test-time compute addresses this limitation by providing the model with additional computational resources and time for structured reasoning, hypothesis testing, condition verification, and answer validation. This process significantly improves accuracy for complex reasoning tasks, but it requires substantially greater computational resources. Whereas earlier improvements in AI capabilities depended almost exclusively on the training phase, they now increasingly arise from both training and inference, as illustrated in Fig. 3.

A variety of techniques have been developed to improve model performance during test-time compute. Chain-of-Thought (CoT) prompting instructs LLMs to reason step by step, generating intermediate reasoning traces and verifying them to arrive at more logical answers. Tree-of-Thought (ToT) methods extend this approach by exploring multiple reasoning paths in parallel, self-evaluating outcomes, and choosing the most promising course of action. These strategies can markedly improve results for tasks involving mathematics, logic, or planning. However, the trade-off is steep: inference compute requirements rise dramatically. Even simple text-based reasoning may consume hundreds of times more

Fig. 3 Metaphor for AI model training, including Training Compute and Test-Time Compute

compute than earlier inference methods, while highly complex problems may require thousands or even hundreds of thousands of times more compute.

The most significant implication of this phase is the projected surge in demand for inference compute as AI usage expands. Currently, the AI ecosystem remains in its infancy, with an estimated 200-300 million daily active users (DAU) [43] [44] [45]. Most applications are still limited to relatively simple functions such as question answering, information retrieval, summarization, programming assistance, and content generation. Truly widespread and sophisticated use of AI in work, daily life, and physical environments has yet to begin. Looking ahead, if a substantial fraction of the world's 8 billion people were to rely on AI-with billions or even trillions of agents providing services and countless robots operating across a wide range of vertical domains—the demand for inference compute would grow exponentially. As AI applications penetrate every industry and daily activity, the frequency and intensity of inference will rise sharply, making it foreseeable that AI inference will require extraordinarily large-scale computational resources.

Phase 3: Explore AI Capability Beyond a Single LLM (Agentic AI, Physical AI)

In the previous two phases, techniques were primarily developed to enhance performance within a single LLM. By contrast, **Phase 3 aims to achieve capabilities that extend beyond the boundaries of a single model.**

There are two main trajectories. The first is to extend LLMs with additional functionalities, effectively transforming them into AI agents. This approach enhances their ability to process information, interact with external systems, and take autonomous actions—strengthening their role in the emerging knowledge-driven economy. This trajectory corresponds to

Physical Economy (Atoms, Photons)

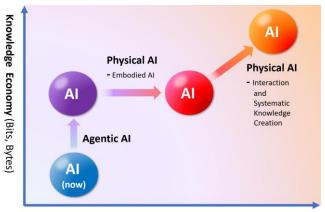

Fig. 4 AI Evolution Trends: Agentic AI and Physical AI

Agentic AI, which primarily engages Layer 5 (Agent Layer) and Layer 6 (Orchestrator Layer), where multiple agents must be coordinated at scale.

The second trajectory is **Physical AI**. Rather than focusing solely on digital knowledge processing, Physical AI expands AI's role into the physical world. It extends computing from the digital domain into the physical domain, enabling applications such as robotics, autonomous vehicles, and intelligent devices at **Layer 7** (**Application Layer**). Importantly, Physical AI not only acts upon the physical environment but also collects data through real-world interaction. This feedback loop strengthens the training process, supporting the construction of more powerful neural networks and feeding improvements back into the **Layer 3** (**Neural Network Layer**).

Fig. 4 provides a conceptual illustration of this trajectory. The vertical axis represents contributions to the knowledge economy (bits, bytes), while the horizontal axis represents engagement with the physical economy (atoms, photons) [46]. At the lower left, today's AI (blue) remains largely confined to the digital knowledge domain. The first transition is toward Agentic AI (purple), where AI systems gain memory, reasoning, planning, and interactive capabilities, enabling them to act autonomously and collaborate with humans or other agents. From there, AI progresses into Physical AI (red), representing embodied intelligence capable of interacting directly with the physical world through robotics, sensors, and actuators. This stage bridges the knowledge and physical economies. The trajectory then advances toward a more mature form of Physical AI (orange), where embodied systems not only act in the world but also generate new knowledge through experimentation, observation, continuous learning.

Together, these stages illustrate how AI is expected to evolve beyond model-centric architectures into an integrated force across both virtual and physical domains, driving future productivity and innovation. In the following sections, we will discuss Agentic AI and Physical AI in greater detail.

# 1) Agentic AI

Consider the example of a student who has graduated with excellent grades and obtained a position at a company. To ensure long-term success in their career, is it sufficient to focus solely on their academic performance? Or must we also cultivate their understanding of organizational processes, teamwork, project execution, and interpersonal communication skills?

A similar reflection applies to large language models (LLMs). When deployed in the real world, do we only need a chatbot that can provide immediate answers, or do we require an AI system capable of solving complex problems? If the goal is the latter, then it is clear that an effective AI system requires more than an LLM alone. Instead, additional

capabilities must be integrated to transform the LLM into a **problem-solving system**. This is the central purpose of **Agentic AI**. In general, AI agents are LLMs augmented with complementary functions such as long-term and short-term memory, reasoning and planning, external tool use, and interaction with the environment.

A common misunderstanding is that LLMs alone represent the entirety of artificial intelligence. This overlooks the fact that users demand **applications that solve real problems**, not the models themselves. Just as people seek reliable transportation rather than an engine, users require AI systems that deliver solutions, without needing to understand the internal specifications of the underlying model. In practice, the integration of LLMs into agents will likely be handled by professional developers and organizations, who—similar to automobile manufacturers—design standardized, safe, and specialized AI agents for different purposes.

In the future, therefore, professional providers will deliver a variety of agent types, each embedding LLMs with the necessary capabilities for their target use cases. This transformation marks the essence of Agentic AI.

## a) Agentic Swarm

Consider the case of founding a high-tech company. Should one seek "the one"—a single, all-knowing genius who manages every aspect of the enterprise, from R&D to manufacturing, finance, marketing, and sales? Or should one instead recruit diverse specialists and assign them distinct roles to handle different functions? In practice, the latter is far more effective: organizations succeed by leveraging collaboration among experts with complementary skills, rather than relying on a single generalist.

A similar principle applies to AI systems. For most applications, there is no need to pursue a single, all-powerful "generalist AI." Instead, integrating multiple specialized AIs can yield more comprehensive and effective results.

An **Agentic Swarm** [47] consists of a collection of AI agents, each with complementary strengths, working together to achieve higher performance. This approach systematically expands AI capabilities by first converting individual LLMs into agents with enhanced functions, and then interconnecting these agents into a network-like swarm.

#### For example,

Fig. 5 illustrates an Agentic Swarm in the context of a travel agency. When a user wishes to plan an overseas trip, the agency's operations are managed by a swarm of AI agents specializing in customer interaction, itinerary planning, marketing, finance, supplier management, and legal compliance. While such a swarm may still collaborate with human employees for oversight and authority, it is conceivable

that in the future all services could be delivered autonomously by AI agents. Planning requires coordination with external entities—airlines, hotel groups, and local service providers—each of which may themselves be managed by separate swarms of AI agents. Across the entire process, airfare, accommodation, transport, restaurants, and tickets are arranged collaboratively by agents, with purchases finalized upon user approval. Additional services, such as hiring a local guide, can also be fulfilled through specialized swarms.

This model is highly **scalable**. Agentic Swarms can collaborate across industries—such as restaurants, railways, or retail—and they can also foster innovation through competition. Multiple swarms operating in the same sector, for example competing travel agencies, could differentiate themselves by specialization: one might focus on cultural tours rooted in fine arts and heritage, while another offers adventure tours based on expertise in mountaineering. Competitive swarms would attract more users, building reputation through demonstrated performance and reliability.

At a broader level, this architecture has the potential to **reshape entire industries**. Services and transactions may migrate into AI-driven ecosystems operated by swarms of agents, handling planning, decision-making, procurement, and commerce. Such ecosystems could eventually supplant many functions traditionally carried out through physical transactions or internet-based e-commerce.

Fig. 5 An example of Agentic Swarm

#### b) AI-based Ecosystem

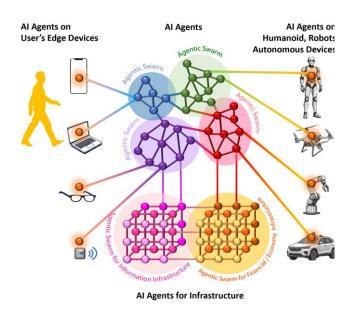

Fig. 6 illustrates a conceptual view of the future AI-based ecosystem. In this ecosystem, diverse AI agents will be organized into different **Agentic Swarms** to provide specialized functions. It is termed an "AI-based ecosystem" because it encompasses not only AI agents but also users, their devices, robots, autonomous systems, and supporting infrastructure such as information flows, financial networks, logistics, and physical facilities. All of these elements collectively form the ecosystem.

The connections among AI agents are highly dynamic rather than permanently fixed. Links are established on demand, and decisions about maintaining persistent communication channels are made on a case-by-case basis. Furthermore, the LLMs embedded within agents may be either dedicated or shared: the same underlying LLM can be configured with different functions to create distinct agents, while multiple agents can also share a common LLM.

The operational flexibility of AI agents is a defining feature of this ecosystem. Agents and swarms may run in cloud data centers, sharing compute resources through time-sharing or parallel execution. Multiple swarms can operate concurrently within a single data center. For distributed computing, agents can be deployed on edge servers closer to users, enabling low-latency services. For security-sensitive applications, they may be deployed on on-premises infrastructure within companies, banks, factories, or research institutions. In addition, governments and enterprises will develop domain-specific infrastructures—spanning information, financial, healthcare, and public services—that form the foundation for sovereign AI.

Fig. 6 An Example of AI-based Ecosystem

AI agents will also reside on **edge devices** such as smartphones, computers, smart glasses, and other AI-enabled devices [48]. These agents act as the human–machine interface, interpreting user intent, mediating communication with external agents, and safeguarding privacy. By leveraging onboard sensors—cameras, microphones, touchscreens, accelerometers—they can assess user status, intentions, and environmental context to provide more personalized and relevant interactions. Moreover, when users initiate AI tasks, edge agents can handle **authorization and access control** before actions are executed in the broader ecosystem.

In parallel, AI agents will be embedded in **physical systems** such as humanoid robots, industrial robots, autonomous vehicles, and specialized machines. These agents will interact bidirectionally with the AI ecosystem, both receiving guidance from swarms and contributing data and actions back to the system. Collectively, such integration will blur the boundary between digital and physical domains, resulting in a pervasive AI-based ecosystem that spans virtual services and real-world operations.

#### 2) Physical AI

Physical AI has two key implications. First, it represents the extension of AI into the physical world, often referred to as Embodied AI [49]. Second, it encompasses the capacity of AI systems to interact with the real world in ways that enhance their intelligence through exploration, experimentation, and feedback. Ultimately, by engaging in systematic learning and knowledge creation within the physical environment, AI can contribute to expanding human understanding of the world.

## a) Embodied AI

**Embodied AI** refers to AI systems equipped with the ability to directly perceive and act in the physical world through sensors and actuators. By having a physical form, these AI agents can perceive their surroundings, take action, and collaborate with humans and other agents in real environments.

There are various types of embodied AI, including autonomous vehicles, drones, industrial robots, quadrupedal robotic dogs, and humanoid robots. Among them, humanoid robots—with their human-like appearance and kinematic structure—are particularly well suited to environments designed for humans, as they can naturally adapt to existing workspaces, tools, and workflows.

#### b) Systematic Knowledge Creation

Beyond embodiment, Physical AI also implies the capacity for **systematic knowledge creation** through direct interaction with the real world. By engaging in exploration and experimentation, AI systems can enhance their intelligence and capabilities in ways that complement data-driven training.

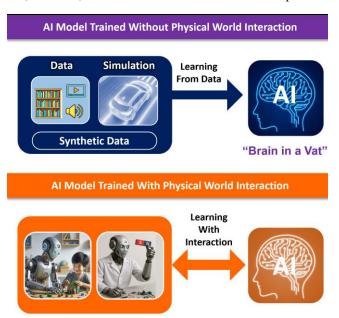

Current AI models are primarily trained on large datasets collected from the Internet, sensors (e.g., driving data from vehicles), or synthetic sources. They may also be trained in simulation environments, such as those developed for autonomous driving. However, under such training paradigms, the model remains effectively **isolated from the real world**. This situation resembles the thought experiment known as the "Brain in a Jar" [50], where the brain is cut off from direct physical interaction and can only acquire knowledge from mediated inputs. This approach fundamentally differs from learning that arises from embodied, physical interaction with the natural world (Fig. 7). Several limitations arise from this isolation:

- Lack of real-world experience and interaction: Purely data-based training (e.g., learning physical properties through videos) can help models capture basic phenomena such as motion, gravity, and Newtonian dynamics, but requires massive amounts of video data. In contrast, humans achieve such understanding far more quickly through simple physical interaction. Moreover, certain properties—such as magnetism or electricity—cannot be easily conveyed visually, limiting the effectiveness of data-only training.

- Difficulty distinguishing fiction from reality: Many real-world events involve intention, deception, or hidden causes. Video data alone often cannot reveal these subtleties. Furthermore, large portions of online content—such as magic shows, fantasy films, or science fiction—are explicitly fictional. Humans can leverage real-world experience to discern fact from fiction, but AI models trained solely on data struggle to make such distinctions.

- Absence of multi-sensory and interactive input: Human learning involves more than vision and hearing. For example, even the simple act of picking up a cup integrates tactile feedback, grip control, joint and muscle coordination, weight perception, and visual monitoring of liquid motion to avoid spillage. This multi-sensory integration is especially important for robots with high degrees of freedom (DoF), such as humanoids with 40–50 DoF, where learning from video alone is insufficient.

- Limitations of simulation: Simulation environments allow controlled practice and the generation of rare scenarios (e.g., hazardous driving conditions), but they remain approximations. More realistic simulations require

exponentially greater compute, yet still cannot replicate the full richness of real-world phenomena. Ultimately, even the most advanced simulation is not equivalent to reality.

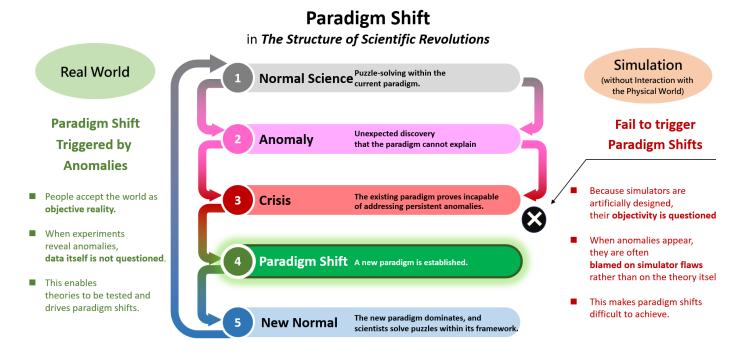

Furthermore, as Kuhn emphasized in his influential book *The Structure of Scientific Revolutions* [51], **paradigm shifts** are essential to the advancement of human knowledge. Scientific understanding does not progress linearly; rather, it evolves through the discovery of anomalies that challenge existing theories, ultimately leading to new paradigms. As shown in Fig. 8, continuous engagement with the real world can expose such anomalies, prompting scientists to question established frameworks and thereby drive scientific progress.

For humans, the conviction that the physical world exists objectively is fundamental to this process. When anomalies arise in experiments, once we are confident that the experimental setup is sound, we tend to revise the theoretical model instead of dismissing the observed data. This openness to questioning theories rather than reality itself enables paradigm shifts and fuels scientific advancement.

By contrast, if future AI systems are trained exclusively in simulated environments without real-world interaction, anomalies observed during "experiments" would likely be attributed to imperfections in the simulation. In such cases, existing theoretical models would remain unchallenged, making paradigm shifts far less likely. Consequently, the growth of AI knowledge would be limited to the boundaries of current human science.

If, however, AI is allowed to interact with and experiment

Fig. 7 Illustration for AI Model Training with and without Physical World Interaction

in the physical world, it could move beyond the "brain in a jar" metaphor [50]. Through embodied exploration and systematic knowledge creation, AI may help extend human understanding and accelerate scientific discovery.

Fig. 9 illustrates the evolution of AI capabilities across Phases 1 to 3. To date, model performance has been enhanced primarily through techniques such as pre-training, fine-tuning, test-time compute, and agentic AI. Looking ahead, **Physical AI** could mark a new stage, enabling AI systems to expand beyond data-driven simulations and engage directly with the physical world. Such interaction may empower AI to assist humanity in exploring new frontiers of knowledge.

At present, however, we remain in the early stages. Agentic AI is only beginning to mature, AI-based ecosystems are still nascent, and Physical AI has been applied only in limited domains such as self-driving cars and robotics. The path toward truly interactive, knowledge-creating AI remains long, underscoring both the challenges and opportunities that lie ahead.

Phase 3 extends AI capabilities beyond individual LLMs toward system-level intelligence. Through Agentic AI, LLMs are augmented with memory, planning, tool use, and interaction abilities, forming the foundation of the Layer 5 Agent Layer. At larger scales, Agentic Swarms emerge, coordinated by the Layer 6 Orchestrator Layer, to deliver

integrated services across industries. Finally, Physical AI introduces embodied and interactive intelligence, linking digital computation with the physical world and shaping applications at the Layer 7 Application Layer. Together, these developments represent a transition from model-centric AI to ecosystem-centric AI, pointing toward the long-term trajectory of artificial intelligence.

## D. Summary for Evolution of Large Language Model

The evolution of large language models can be understood through three progressive phases. Phase 1 focused on scaling training compute, driving exponential growth in model size and capability. Phase 2 emphasized test-time compute, enabling advanced reasoning and inference through advanced reasoning and novel inference-time techniques. Phase 3 extends AI beyond single models toward Agentic AI, swarms, ecosystems, and Physical AI, integrating intelligence across both digital and physical domains to form AI-based ecosystems. Together, these phases highlight the shift from model-centric scaling to ecosystem-centric intelligence, underscoring the growing importance of coordination, embodiment, and real-world interaction in shaping the future trajectory of AI.

Fig. 8 Paradigm Shifts in the Real World may be Difficult to Occur in the Simulated World.

#### IV. EVOLUTION FOR EACH LAYERS (BOTTOM-UP VIEW)

Section III provided a **top-down view** of AI compute evolution, showing how the seven layers jointly advanced across three phases to enable system-level capability growth. In contrast, Section IV offers a **bottom-up view**, focusing on the distinct evolution within each individual layer, particularly Layers 1–4. Together, these complementary perspectives highlight both the overall trajectory and the layer-specific innovations.

#### A. Evolution of Layer 1 Physical Layer

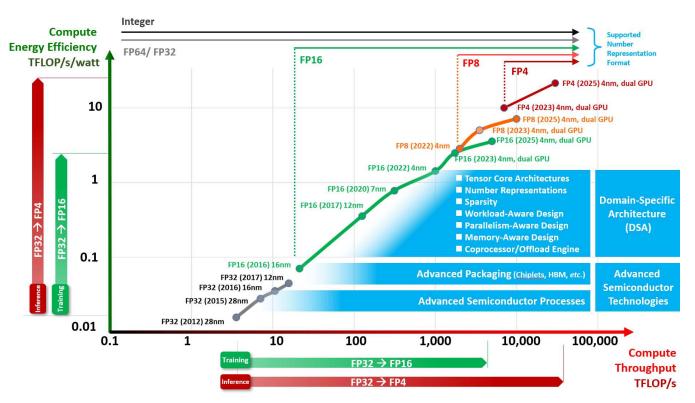

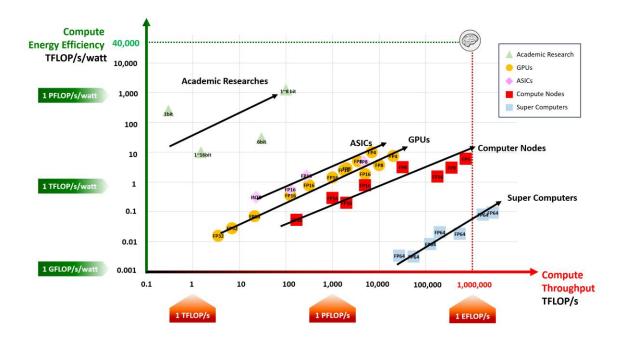

The Physical Layer provides the hardware foundation of AI computing, encompassing semiconductor integrated circuits (ICs) that execute computations. To illustrate the "Scale-Up" trajectory, Fig. 10 shows the evolution of GPUs from 2012 to 2025, with Nvidia data-center GPUs (from K20x [52] to GB300 [53]) used as representative examples. The X-axis denotes compute throughput in TFLOP/s (tera floating-point operations per second, and 1 Tera= 10<sup>12</sup>), while the Y-axis indicates compute energy efficiency in TFLOP/s per watt. Both axes are plotted on a logarithmic scale to highlight long-term trends.

GPU evolution demonstrates continuous improvement in both computing power and energy efficiency. Four major drivers can be identified:

(1) Advanced Semiconductor Processes. From 2012 to 2025, GPU manufacturing nodes advanced from 28 nm to 3 nm, with 2 nm technology now available and further scaling toward the Å (Ångström) era on the horizon. These advances significantly enhanced compute performance, improved energy efficiency, reduced circuit dimensions,

Fig. 9 Illustration of Evolution of AI Capability (Current Status and Forecast)

and increased transistor density. However, process scaling alone is insufficient to meet the rapidly growing demand for AI computing. Moreover, the pace of Moore's Law has slowed, with each successive node delivering smaller incremental gains. As a result, continued progress increasingly depends on innovations in IC design, beyond what process technology alone can provide.

(2) Advanced Packaging. In addition to process scaling, advanced packaging technologies have played a critical role in boosting AI computing performance. High-Bandwidth Memory (HBM) has been widely adopted to increase data throughput and mitigate system bottlenecks, enabled by packaging innovations such as CoWoS (Chipon-Wafer-on-Substrate), which provide high-density, high-speed interconnects with extremely wide data buses between compute and memory dies.

Advanced packaging also mitigates the *reticle limit*—the maximum chip area that can be fabricated in a single lithography exposure, currently around 858 mm² for standard equipment. By connecting multiple chiplets into a unified system, packaging techniques enable larger effective chip areas and greater functional integration, which is particularly valuable for AI workloads that demand massive compute resources.

Looking ahead, emerging packaging approaches such as SoIC (System-on-Integrated-Chip), SoW (System-on-Wafer), and 3DIC (three-dimensional integrated circuits) hold significant potential to further enhance compute density, bandwidth, and overall system performance. These innovations are expected to play a central role in scaling AI computing beyond the limits of traditional monolithic design.

(3) **Tensor Core Architecture.** Before the rise of AI workloads, most processor computations were executed using scalar, vector, and SIMD (single-instruction multiple-data) operations in CPUs, GPUs, and DSPs. However, AI workloads are uniquely demanding, dominated by large-scale matrix and tensor operations. This created the need for architectures that could deliver higher efficiency and throughput for dense linear algebra.

This led to the development of Tensor Core architectures, often implemented as systolic arrays, which perform matrix multiplications and accumulations in a highly parallel and energy-efficient manner. Tensor Cores have since become a central feature of modern AI hardware, appearing in domain-specific ASICs such as Google's TPUs (Tensor Processing Units), as well as in GPUs and other dedicated AI accelerators in ASICs. By aligning hardware more closely with the computational structure of neural networks, Tensor Cores have significantly advanced both performance and energy efficiency in AI computing.

- (4) Number Representation. Low-bit numerical formats reduce circuit area, latency, and power consumption [54], though at the expense of numerical accuracy. Before the rise of AI computing, the dominant format was FP32 (32bit floating point), with FP64 used in supercomputers for high-precision scientific computation. As AI workloads grew, 16-bit formats such as FP16 and BF16 (Brain Floating Point 16-bit) [55] [56] were adopted for training due to their superior speed and energy efficiency. More recently, ultra-low-precision formats such as FP8 [57] and FP4 [58] have been introduced for inference, where slight accuracy degradation is tolerable or can be mitigated through mixed-precision training. In addition, integer-only inference can be realized through quantization schemes to reduce the size to improve inference latency and throughput [59] [60]. Overall, number representation has become a critical design parameter, balancing accuracy, performance, efficiency, and implementation cost in AI hardware.

- (5) Sparsity. Sparsity is an important property of neural networks. After training, many parameters often become zero or near zero, allowing sparsity-aware computation to significantly reduce unnecessary multiplications and memory usage. This property can be exploited to save computation and improve energy efficiency. Techniques such as *pruning* can further remove redundant connections [61]. Sparse neural networks can achieve comparable

accuracy with far fewer operations [62], making them particularly attractive for efficient AI hardware.

To fully leverage sparsity for computational efficiency, hardware support is crucial. Early designs such as MIT Eyeriss [63] implemented hardware-aware sparsity acceleration, while more recent NVIDIA GPUs employ structured 2:4 sparsity (50%) patterns to double the effective throughput of dense matrix units [64] [65]. Beyond model parameters, data itself can also exhibit sparsity. For example, Google TPU's SparseCores [66] are dataflow processors that accelerate models using sparse operations to optimize irregular data workloads.

(6) Workload-Aware Design. Training-oriented inference-oriented workloads exhibit fundamentally different characteristics and design strategies [67].. involves long-duration, high-intensity Training computation on pre-prepared datasets with predictable compute patterns. The primary objective is to minimize total training time, which typically leads to large batch sizes and high-throughput operation.

In contrast, inference must handle dynamic workloads where users are latency-sensitive. Consequently, inference optimization focuses on different objectives:

(i) Interactive Serving Performance — measuring the perceived responsiveness of the model. Common

Fig. 10 Scale-Up Evolution of Semiconductor IC (Single chip of GPU for example)

benchmarks include *Time-To-First-Token (TTFT)* and *Time Per Output Token (TPOT)* [68] [69].

- (ii) **Batch Processing Performance** monitoring system behavior under varying workloads. Benchmarks include overall throughput at different batch sizes, latency and its variance, and how these metrics scale with increasing system load [67].

- (iii) **Mixture-of-Experts (MoE) Support** enhancing inference performance in MoE-based LLMs [70] by managing conditional computation, sparse activation patterns, and distributed expert networks across devices [48].

- (iv) **Deployment Support** enabling flexible inference deployment strategies, such as *Speculative Decoding* [71] [16], which generates low-latency responses using distilled smaller LLMs and verifies outputs with full-sized models, as well as distributed inference systems spanning from data centers to edge devices [48].

- (7) Parallelism-Aware Design. Most AI accelerators exploit parallelism at multiple levels and granularities [72].. Hardware support for parallelism is crucial to boosting performance and achieving high utilization. There are two major types: Data parallelism and Model parallelism. Common Model parallelism techniques include:

- (i) **Pipeline Parallelism** Divides a model into several stages, executing layers across multiple processing units in parallel and overlapping computation with communication to reduce pipeline bubble [73].

- (ii) **Tensor Parallelism** Distributes tensor parameters within each layer across multiple processing units, providing an additional orthogonal dimension for model partitioning [74].

- (iii) **Expert Parallelism** Distributes experts in *Mixture-of-Experts (MoE)* architectures across processing units to support efficient parallel execution [75].

- (8) Memory-Aware Design. In AI computing, memory is as crucial as computation itself. If data cannot be supplied in time, compute units remain idle regardless of processing capability. Hence, memory hierarchy, capacity, bandwidth, and scheduling are key considerations in hardware architecture. Memory-aware design techniques include:

- (i) Cross-Hierarchy Memory Management. Beyond on-die memory, on-package memories such as High Bandwidth Memory (HBM) [76] [77] and emerging Compute Express Link (CXL)-attached memory [78] [79] provide high-capacity, high-bandwidth options. Efficient

- management across these heterogeneous memory tiers, including off-chip memory, is essential to optimize performance.

- (ii) Cache and Context Management. Optimization methods include pre-fill [80] and pre-fetch [81] techniques for key-value (KV) caches, cache offloading [82], and dynamic resource management for varying context lengths [83].

- (iii) **Compression.** Memory compression techniques include cache compression [84] and model compression through quantization, pruning, knowledge distillation, and low-rank factorization [85]. Further compression can be applied to model weights and activations in LLMs [86].

- (iv) Compute-Near-Memory and Compute-in-Memory. The data movement bottleneck between processors and memory known as the "memory wall" [87] or the "von Neumann bottleneck" [88] is particularly severe for LLM workloads with massive parameters and data transfers. Research efforts have explored Compute-Near-Memory (CNM) and Compute-in-Memory (CIM) architectures to mitigate these limitations [89] [90].

- (9) Coprocessor/ Offload Engine. When a single AI accelerator faces excessive computational or memory demand, additional coprocessors or offload engines can complement the main chip. In large-scale inference, the context length can exceed one million tokens, causing distinct bottlenecks: the context phase is compute-bound, while the generation phase is memory-bandwidth-bound. To address this, specialized GPU variants such as NVIDIA Robin CPX [91] target specific workloads. Other strategies include CPU offloading for activation data [92], and CXL-based offloading for memory extension. Because Compute Express Link (CXL) allows devices to access each other's resources without host intervention, model parameters or activations that exceed GPU memory can be offloaded to CPU-attached CXL memory, effectively mitigating memory bottlenecks [82] [93].

Among these technologies, advanced process nodes and advanced packaging belong to semiconductor manufacturing innovations, while tensor core architectures, number representations, sparsity, workload-aware, parallelism-aware, memory-aware, and coprocessor/ offload engine designs fall under the domain of domain-specific architectures (DSAs). DSAs enable joint hardware—software—system co-optimization for AI algorithms, setting the trajectory of AI accelerators apart from traditional general-purpose processor architectures.

As shown in Fig. 10, between 2012 and 2025, FP16 computation—widely used in AI training—delivered roughly a 1,000× increase in throughput and a 100× improvement in energy efficiency per GPU. In contrast, ultra-low-precision formats such as FP4, applied in inference workloads and optimized through arithmetic techniques, have the potential to achieve up to a 10,000× gain in throughput and a 1,000× gain in efficiency per device, provided that accuracy remains acceptable. These results underscore how design parameters within DSA, exert a decisive influence on overall system performance. Energy efficiency is more difficult to scale than throughput performance. Improvements in energy efficiency have trailed throughput gains by approximately an order of magnitude on a logarithmic scale, highlighting a fundamental challenge for sustainable AI hardware development.

## B. Evolution of Layer 2 Link Layer

The Link Layer comprises the system hardware and software that interconnects and manages the compute elements in Layer 1. To meet the massive demands of AI workloads, both Scale-Up (vertical performance improvements) and Scale-Out (horizontal performance expansion) strategies are required. In practice, large-scale AI systems increasingly rely on Scale-Out, with modern data centers already connecting hundreds of thousands of chips—and potentially millions in the near future—to deliver the required compute capacity.

Fig. 11 illustrates the architectural strategies of Scale-Up

and Scale-Out for expanding AI computing capacity. On the left, the Scale-Up approach focuses on enhancing performance within a single compute node. This begins at the chip level, where chip dies can be scaled through DSA design and advanced semiconductor processes, and then multiple compute dies and memory dies can be integrated into larger chip packages or even wafer-scale devices [94] [95]. These chip dies are then interconnected within a package through highbandwidth interconnects, further extended by scale-up networks inside compute nodes [96]. On the right, the Scale-Out approach expands capacity by linking multiple compute nodes into large-scale clusters within a data center, and further across multiple data centers (Scale-Across). Scale-Out provides extreme performance through massive parallelism, but often at the cost of greater energy consumption and communication overhead. Together, these strategies, Scale-Up improving chip and node-level performance, and Scale-Out extending to system and cross-data-center integration, form the foundation of modern hyperscale AI infrastructure.

Achieving this scale requires a combination of sophisticated architectural design, high-bandwidth interconnects, robust software frameworks, efficient power and cooling systems, and comprehensive operational strategies. Building hyperscale AI data centers is therefore an extremely complex engineering challenge.

Fig. 11 Scale-Up, Scale-Out Strategies for expanding AI computing capacity

# 1) Impact of Scale-Up and Scale-Out on AI Computing Power and Energy Efficiency

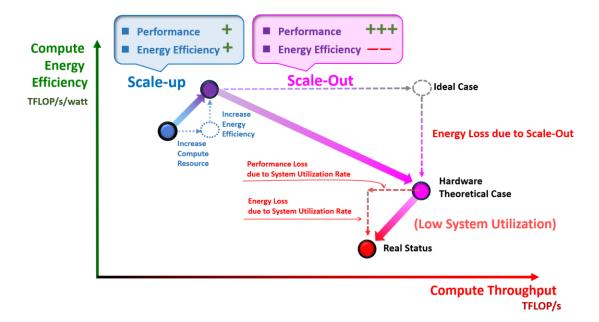

Scale-Up and Scale-Out both increase computing capacity, but they also impose additional system burdens, often reducing overall energy efficiency (Fig. 12). The analysis is as follows:

- (1) Scale-Up. Scaling up enhances performance through three key approaches: (i) improving individual chips via advanced process technologies and design innovations, (ii) integrating multiple dies within a single package, and (iii) interconnecting multiple chips inside a compute node, as illustrated in the left part of Fig. 11. Energy efficiency may also benefit from semiconductor process advances and domain-specific architectures (DSAs) in IC design, as shown in Fig. 10. In addition, optimized high-speed interconnects between dies and chips are critical since they directly impact both performance and efficiency".

- (2) Scale-Out. Scaling out expands computing capability by linking large numbers of chips—ranging from dozens to hundreds of thousands, and potentially millions in the future-across compute nodes, racks, clusters, and even geographically distributed data centers. This horizontal expansion dramatically amplifies aggregate performance but introduces challenges: high-speed interconnects for node-to-node. rack-to-rack. and cluster-to-cluster communication consume substantial energy, increased data movement across long interconnect paths adds latency bottlenecks. Thus, scale-out delivers raw performance gains but often at the expense of energy efficiency. Technologies that mitigate the energy overhead of large-scale interconnection are essential for sustainable AI progress.

- (3) System Utilization. Even when theoretical capacity is increased through Scale-Up and Scale-Out, real-world utilization often falls short. Data dependencies and delivery delays create "bubbles" in the compute pipeline, leading to idle cycles that waste energy and reduce throughput. To address this, techniques such as caching, batching, pipelining, and prefetching [96] [97] [98] are used. For example, data centers may aggregate tasks across workloads via batch processing to improve GPU or ASIC utilization—though at the cost of higher latency per task. Ultimately, utilization is a decisive factor in determining how much of the theoretical performance and efficiency can actually be realized at scale.

- (4) Software Frameworks. In addition to hardware scaling, software frameworks that orchestrate multi-GPU and multi-node systems are equally critical to the effectiveness of the Link Layer. For training, frameworks like Megatron-LM [99] enabled efficient scaling of LLMs to thousands of GPUs through tensor, pipeline, and data parallelism. Building on this foundation, state-of-the-art systems now extend scaling to tens or even hundreds of thousands of GPUs, enabling the training of trillionparameter models. For inference, inference platforms like Dynamo [100] provide a high-throughput low-latency framework for deploying AI models at scale in distributed environments. In addition, the Key-Value (KV) cache, storing past keys and values for the attention mechanism, emerges as a critical bottleneck in both memory usage and latency. Many researches toward KV-cache, such as vLLM [101], an LLM serving system for near-zero waste in KV-cache memory and flexible sharing of KV cache, reducing KV-cache size with cross-layer attention [102], layer-condensed KV-Cache KV-cache [103] and

Fig. 12 The Impact of Scale-Up and Scale-Out on AI Computing Performance and Energy Efficiency

compression [104]. Overall, the synergy of hardware and software in Layer 2 advances the compute platform, enabling the practical deployment of large-scale AI across both training and inference stages.

As shown in Fig. 12, performance and energy efficiency are both critical parameters in the Scale-Up process, as they directly define system capability. While Scale-Out substantially increases aggregate performance, the power consumption of inter-node communication—whether between racks, across clusters, or spanning data centers—imposes significant limits on energy efficiency. Consequently, technologies that reduce the energy cost of large-scale interconnection will be essential for sustaining progress in AI computing.

This trade-off highlights the central role of the Link Layer: it must deliver scalable, reliable, and energy-aware interconnect architectures to support the next generation of AI systems.

## 2) Evolution of AI Compute

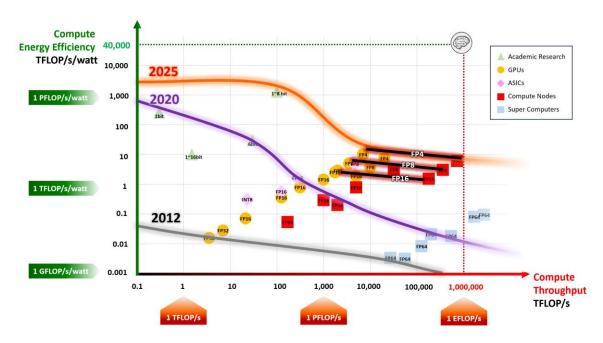

Fig. 13 illustrates several categories of AI computing systems to highlight their evolution over time. Five categories are shown:

- GPUs (e.g., Nvidia GPUs [52] [53]), shown as orange circles

- ASICs (e.g., Google TPUs [105] [66] [106]), shown as pink diamonds.

- **Compute Nodes** (e.g., Nvidia DGX systems [107] [108]), shown as red squares.

- **Supercomputers**, represented by the top-ranked systems on the Top500 list [109] [110], shown as blue squares

- Academic research prototypes, reported in research papers [111] [112] [113] [114] [115], shown as green triangles.

In Fig. 13, only AI computing systems capable of scaling up to support LLM workloads are shown, in order to highlight mainstream trends. However, several other types of AI computing platforms are not included, such as *FPGAs* [116] [117], *neuromorphic processors* [118], *photonics computing systems* [119] and *quantum AI platforms* [120].

Numerical precision formats (FP64, FP32, FP16, FP8, FP4, INT8) are labeled within the markers. Since modern GPUs typically support multiple formats (e.g., FP16, FP8, FP4), their performance is plotted separately for each. GPU-based compute nodes are treated in the same way. For supercomputers, FP64 is used because the Top500 rankings are based on the Linpack benchmark. In contrast, academic research results are labeled according to their specific bit

formats. For certain specialized approaches, such as photonic computing [65], no numerical precision format is assigned in the figure.

In Fig. 13 the X-axis represents compute throughput (TFLOP/s), and the Y-axis represents compute energy efficiency (TFLOP/s/W), both plotted on logarithmic scales. For reference, the human brain is shown in the upper-right corner. It consumes approximately 25 W of power, derived from an estimated daily energy consumption of 516 kcal [121]:

**516** kcal/day × 4184 J/kcal ÷ 86400 s/day

$$\approx$$

**24**. **99** W (1)

The brain is further estimated to perform on the order of  $10^{18}$  operations per second [122] [123], yielding an energy efficiency of roughly 40,000 TFLOP/s/W.

Fig. 14 depicts the architectural evolution of AI computing across three milestones—2012, 2020, and 2025:

- 2012 (AlexNet). The release of AlexNet, trained on GPUs, marked a breakthrough in deep learning. GPUs quickly became the primary engines for AI training, but at this stage were not optimized for neural workloads. The gray trend line highlights the 2012 landscape, where GPU energy efficiency lagged the human brain by six to seven orders of magnitude.

- 2020 (Transformers and LLMs). The release of the Transformer architecture in 2017, followed by OpenAI's GPT [124] and Google's BERT [125] in 2018, marked the beginning of the era of large language models (LLMs) and drove exponential growth in compute demand. The purple trend line highlights the 2020 landscape, where GPUs and TPUs—optimized through a combination of process scaling and domain-specific architectures (DSAs)—delivered rapid improvements in both performance and energy efficiency.

- 2025 (Current State). The orange trend line highlights today's landscape. The right-hand region reflects extreme compute throughput enabled by scale-out systems interconnecting hundreds of thousands of chips, though with declining efficiency due to interconnect and data movement overheads. The left-hand region represents modest-scale systems, where energy efficiency improves through specialized chip designs (e.g., compute-in-memory) and ultra-low-bit formats (e.g., 1-bit). Notably, GPUs with different number representation (FP4, FP8 and FP16) yield different energy efficiency.

Overall, scaling compute throughput is relatively straightforward via large-scale scale-out clusters, but

improving energy efficiency remains the greater challenge. The human brain sustains advanced intelligence with only ~25 W, whereas today's top-ranked supercomputer consumes ~29.58 MW [126] yet still falls short of brain-level efficiency. This striking disparity underscores the vast headroom for innovation in both neural architectures and AI system design.

In summary, the evolution of the Link Layer underscores a core challenge for AI computing: scaling throughput is achievable, but sustaining energy efficiency is far more difficult. While Scale-Up and Scale-Out drive raw performance, the true bottleneck lies in enabling the Link Layer to deliver scalable, reliable, and energy-efficient interconnects. Overcoming this limitation will be essential for advancing AI systems beyond today's data center scale.

Fig. 13 Evolution of AI Computing Chips and Systems (by Types)

Fig. 14 Evolution of AI Computing Chips and Systems (by Years)

## C. Evolution of Layer 3 Neural Network Layer

The Neural Network Layer forms the core of modern AI systems. Over the past decade, various neural network architectures have been developed, including CNNs, RNNs, LSTMs, and GANs. Today, the dominant architecture is the **Transformer model**, which underpins large-scale language models (LLMs). Another widely adopted architecture is the **Diffusion Model**, which powers generative AI applications such as image, video, and content creation.

LLMs have further diversified into multiple subcategories. Beyond text processing, some LLMs handle multimodal signals such as images, video, audio, and music, and are referred to as multimodal LLMs (or LMMs, Large Multimodal Models) [127]. When combined with computer vision capabilities, they are often termed Vision-Language Models (VLMs) [128]. More advanced systems that integrate vision, language, and action for behavioral control are referred to as Vision-Language-Action (VLA) [129] models. For simplicity, this paper collectively refers to these models as LLMs.

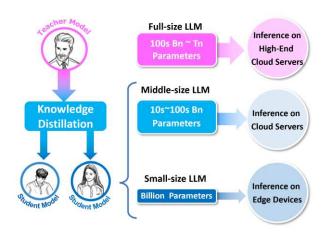

Building on the earlier discussion of Phases 1 through 3, the future evolution of LLMs is not confined to a single trajectory. At least two complementary development paths can be identified, as shown in Fig. 15.

## • Path 1 – Exploring AI Capability:

This path pursues ever-greater intelligence, attracting major investments in compute and cutting-edge research. Companies such as OpenAI, Google, Anthropic, and xAI are pushing toward artificial general intelligence (AGI) [130] or even artificial

**Evolution Path of LLMs** Al Model Complexity ■ Path 1 advances drive Path 2 progress ■ Open-source models accelerate Path 2 ■ Together they make AI more practical, scalable, and accessible [Path 1] Exploring AI Capability Pushing Al performance boundaries with advanced technologies aiming toward AGI and superintelligence [Path 2] Democratizing AI Reducing inference cost while keeping strong capability in compact models: · Lower cloud compute demand • Enable on-prem AI servers Deploy on edge devices · Shrink AI agents for wider use Time

Fig. 15 Two Paths for LLM Evolution

superintelligence (ASI) [131]. However, because training at this scale requires extraordinary computational resources, this path is limited to a small number of well-funded organizations.

# • Path 2 – Democratizing AI:

This path emphasizes broad, practical applications. Most real-world use cases do not require full-scale AI functionality. Instead, **knowledge distillation** [18] techniques are used to derive smaller, more efficient models from large teacher LLMs. Although distillation itself consumes additional compute, the resulting lightweight models dramatically reduce inference costs, power consumption, and hardware requirements. This makes AI more accessible to diverse users and industries. The key benefits include:

- O Reduced energy consumption in cloud servers.

- O Deployment on on-premises servers, reducing risks of sending confidential data to the cloud.

- O The ability for sub-billion-parameter models to run on low-cost hardware and edge devices.

- O Lower resource requirements for building AI agents, facilitating the growth of agent-based ecosystems.

The two paths reinforce each other: as Path 1 produces increasingly capable LLMs, Path 2 benefits by distilling those capabilities into smaller, more practical models.

Fig. 16 illustrates this with an analogy. Path 1 produces full-scale models, just like professors with encyclopedic knowledge across science, humanities, business, and the arts, as well as fluency in multiple human and programming languages. However, just as not every task requires a professor, not every AI application requires a full-scale LLM. Through distillation, **student models** can be created:

Fig. 16 Scenarios for LLM Applications: Teacher Model and Student Model

- Medium-sized models (like graduate students) retain broad expertise in selected domains and are suitable for cloud deployment, balancing capability with efficiency.

- Small-sized models (like high school students) focus on narrow subject areas, greatly reducing resource requirements and making them ideal for edge devices.

This dual evolution—toward both cutting-edge research and widespread practical deployment—will define the trajectory of the Neural Network Layer in the coming years.

In summary, the evolution of the Neural Network Layer reflects a dual trajectory. Path 1 continues to push the frontier of AI capability, driving large-scale investments in training ever-larger LLMs in pursuit of AGI and superintelligence. Path 2, in parallel, focuses on democratizing AI through distillation into smaller, more efficient models that enable broad deployment across cloud, enterprise, and edge environments. These two paths are not in conflict but complementary: advances at the frontier feed directly into lightweight models that power practical applications. Together, they illustrate how the Neural Network Layer is evolving from singular breakthroughs into a diverse ecosystem of models—ranging from frontier-scale LLMs to resource-efficient variants—that collectively shape the future trajectory of AI.

#### D. Evolution of Layer 4 Context Layer